Автоматическая оптическая паяльная станция BGA

Широко используется для ремонта материнских плат мобильных телефонов, ноутбуков, компьютеров, телевизоров, кондиционеров и т. д. на уровне микросхем. Он имеет высокий уровень успешного ремонта и высокую степень автоматизации и экономит много человеческих усилий. Мы являемся профессиональным производителем этой машины и имеем ее в наличии на складе.

Описание

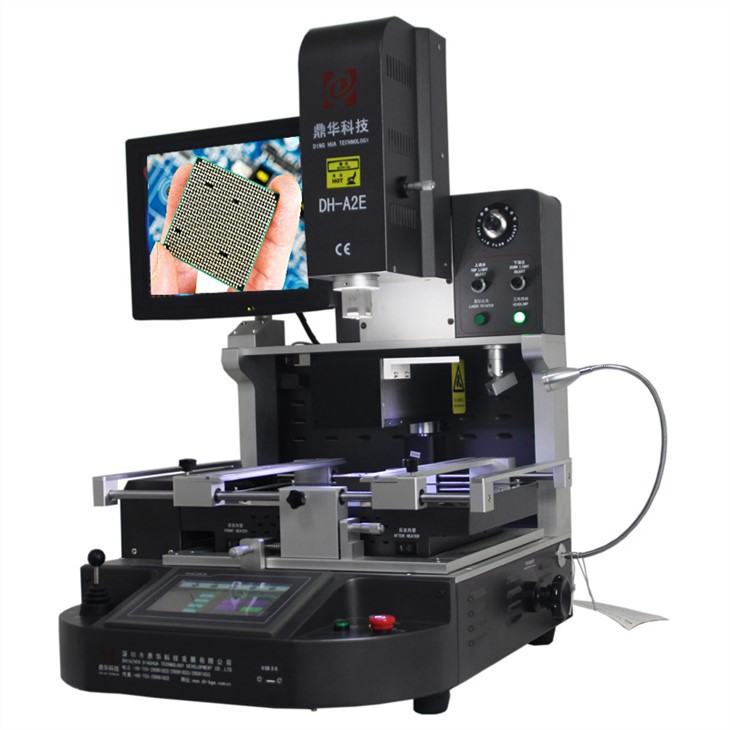

Автоматическая оптическая паяльная станция BGA

1. Применение автоматической оптической паяльной станции BGA

Материнская плата компьютера, смартфона, ноутбука, логической платы MacBook, цифровой камеры, кондиционера, телевизора и других электронных устройств.

оборудование из медицинской промышленности, индустрии связи, автомобильной промышленности и т. д.

Подходит для различных чипов: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, светодиодный чип.

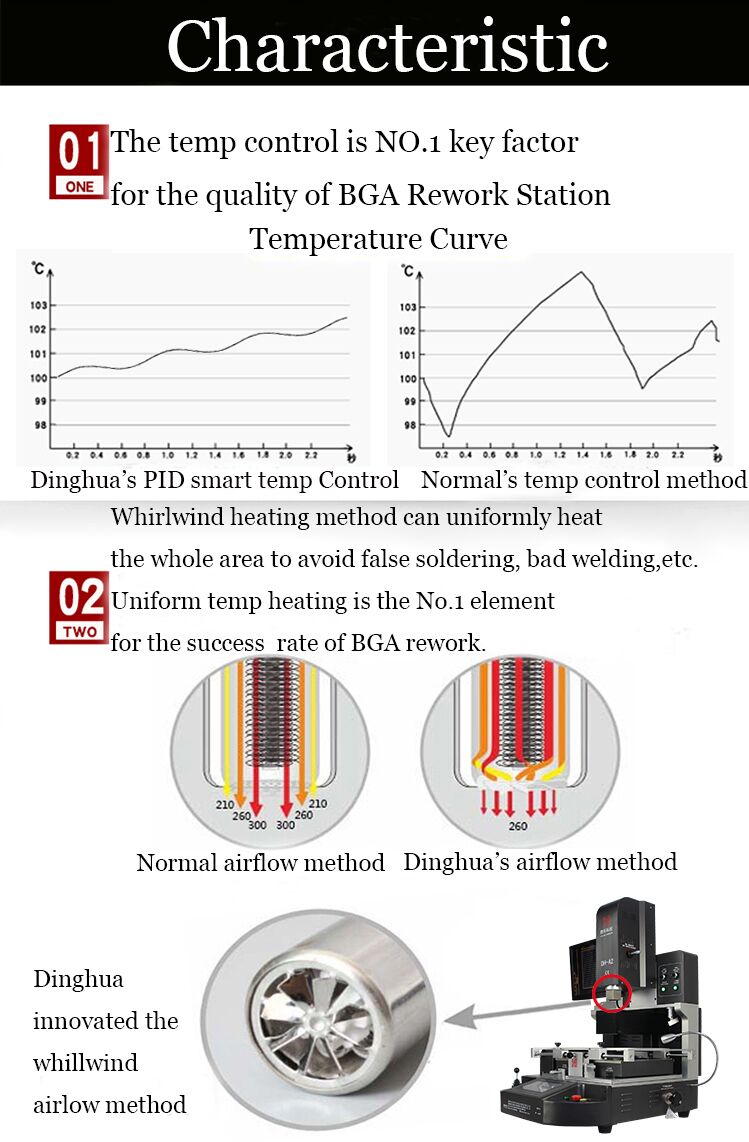

2. Особенности продукта автоматической оптической паяльной станции BGA

•Высокий уровень успешного ремонта на уровне чипа. Процесс распайки, монтажа и пайки осуществляется автоматически.

• Точное выравнивание каждого паяного соединения может быть гарантировано с помощью ПЗС-камеры с оптическим выравниванием.

• Точный контроль температуры может быть обеспечен с 3 независимыми зонами нагрева. Машина может установить и сохранить

1 миллион профилей температуры.

• Созданный вакуум в монтажной головке автоматически собирает BGA-чип после завершения отпайки.

3. Спецификация автоматической оптической паяльной станции BGA

4. Детали автоматической оптической паяльной станции BGA

ПЗС-камера (точная система оптического выравнивания); 2.HD цифровой дисплей; 3. Микрометр (регулировка угла стружки);

4.3 автономные обогреватели (воздушный и инфракрасный); 5. Лазерное позиционирование; 6. Интерфейс сенсорного экрана HD, управление ПЛК;

7. Светодиодная фара; 8. Джойстик.

5.Почему выбирают нашу автоматическую оптическую паяльную станцию BGA?

6.Сертификат автоматической оптической паяльной станции BGA

7. Упаковка и отгрузка автоматической оптической паяльной станции BGA

8.Часто задаваемые вопросы

Как проверить чип?

Первоначальный тест чипа на системном уровне

SoC основан на глубоких субмикронных процессах, поэтому тестирование новых SoC-устройств требует совершенно нового подхода. Поскольку каждый функциональный компонент

имеет свои собственные требования к тестированию, инженер-конструктор должен составить план тестирования на ранней стадии процесса проектирования.

Должен быть реализован план поблочного тестирования устройств SoC: должным образом настроены инструменты ATPG для тестирования логики; короткое время испытаний; новый высокоскоростной

модели отказов и несколько тестов памяти или небольших массивов. Для производственной линии метод диагностики не только находит неисправность, но и выделяет

неисправный узел от рабочего узла. Кроме того, по возможности следует использовать методы тестового мультиплексирования для экономии времени тестирования. В сфере высоко

интегрированное тестирование интегральных схем, тестируемые методы проектирования ATPG и IDDQ имеют мощный механизм разделения неисправностей.

Другие фактические параметры, которые необходимо планировать заранее, включают количество выводов, которые необходимо просканировать, и объем памяти на каждом конце выводов.

Граничное сканирование может быть встроено в SoC, но не ограничивается тестами межсоединений на платах или многокристальных модулях.

Несмотря на то, что размер чипа уменьшается, он по-прежнему может содержать от миллионов до 100 миллионов транзисторов, а количество тестовых режимов возросло до беспрецедентного уровня.

уровней, что приводит к более длительным циклам испытаний. Эту задачу можно проверить. Режим сжатия для решения, коэффициент сжатия может достигать от 20 до 60 процентов. Для сегодняшнего масштабного

конструкции чипа, чтобы избежать проблем с емкостью, необходимо найти тестовое программное обеспечение, которое может работать на 64-разрядных операционных системах.

Кроме того, тестовое программное обеспечение сталкивается с новыми проблемами тестирования, вызванными глубокими субмикронными процессами и увеличивающейся частотой. В прошлом тестовый режим ATPG для

тестирование статических блокирующих ошибок больше не применялось. Добавление функциональных шаблонов к традиционным инструментам затрудняло поиск новых ошибок. Лучший подход заключается в

классифицировать прошлые группы функциональных режимов, чтобы определить, какие сбои не могут быть обнаружены, а затем создать режим ATPG для захвата этих отсутствующих типов сбоев.

По мере увеличения проектной мощности и уменьшения времени тестирования каждого транзистора для выявления проблем, связанных со скоростью, и проверки синхронизации схемы применяется синхронный метод тестирования.

должны быть трудоустроены. Синхронное тестирование должно включать несколько моделей отказов, включая переходные модели, задержки пути и IDDQ.

Некоторые отраслевые компании считают, что наиболее эффективной стратегией тестирования может быть сочетание блокирующих, функциональных и переходных/путевых сбоев. Для глубокого

субмикронные чипы и работа на высоких частотах, тестирование переходных процессов и задержек пути еще более важны.

Для решения проблемы точности АТС при синхронизации тестового ядра и удешевления необходимо найти новый метод, упрощающий интерфейс

тестовое устройство (тестирование переходных процессов и задержек пути требует точных часов на интерфейсе тестового устройства), Это гарантирует, что сигнал будет достаточно точным во время теста.

Поскольку высока вероятность производственного брака в блоке памяти SoC, BIST памяти должен иметь функцию диагностики. Как только проблема обнаружена,

неисправная адресная единица может быть сопоставлена с избыточной памятью резервной адресной единицы, а обнаруженный неисправный адрес будет отброшен. Избегайте сброса

весь дорогой чип.

Тестирование небольших блоков встроенной памяти устраняет необходимость в дополнительных логических элементах или управляющей логике. Например, методы тестирования векторного преобразования могут преобразовать

функциональные режимы в серию режимов сканирования.

В отличие от метода BIST, функциональный вход обходного блока памяти не требует дополнительной логики. Поскольку дополнительная тестовая логика не требуется, SoC

инженеры-разработчики могут повторно использовать тестовые шаблоны, которые были сформированы в прошлом.

Усовершенствованные инструменты ATPG не только параллельно тестируют макросы, но и определяют, есть ли конфликты, а также детализируют, какие макросы можно тестировать параллельно, а какие

макросы нельзя тестировать параллельно. Кроме того, эти макросы можно эффективно тестировать, даже если часы макроса совпадают с часами сканирования (например, синхронная память).

В настоящее время на плотной двухсторонней плате не хватает контрольных точек, и каждый сложный чип должен быть оснащен схемой граничной развертки. Без

сканирование границ, поиск производственных дефектов на уровне платы довольно сложны и даже не могут быть найдены. Благодаря граничному сканированию тестирование на уровне платы становится чрезвычайно простым.

и не зависит от логической схемы внутри чипа. Граничное сканирование также может настроить режим ATPG для сканирования цепи чипа на любом этапе производства.